세계적인 테크니컬 엔지니어링 소프트웨어 공급업체인 매스웍스는 6월 20일 서울 코엑스 인터컨티넨탈호텔에서 엔지니어들을 위한 매스웍스 종합기술 컨퍼런스인 MATLAB EXPO 2012를 개최했다. 이날 매스웍스는 MATLAB과 Simulink에서 동시에 HDL 코드 생성과 검증을 지원한다고 밝혔다.

MATLAB EXPO Korea 2012에서는 매스웍스 본사 프로덕트 마케팅 디렉터인 폴 버나드(Paul Barnard)가 기조 연설자로 나서 ‘Getting to Smart’를 주제로 발표했으며, 고려대학교 최진영 교수가 ‘융합소프트웨어의 새로운 기회’에 대한 초청기조연설을 진행했다.

또한 다양한 고객 사례 및 파트너사의 관련 솔루션 전시, 매스웍스 전문가 및 관련 업계 엔지니어들과의 네트워킹을 통해 실무 정보를 나누는 의미 있는 자리로 진행되어 참석자의 많은 호응을 받았다.

FPGA 설계와 시스템 모델 검증을 자동화

이번 매스웍스 행사에서의 최대 이슈는 MATLAB에서 자동으로 HDL 코드를 생성해 엔지니어가 FPGA와 ASIC 설계를 손쉽게 구현할 수 있도록 지원하는 새로운 버전의HDL Coder의 발표이다. 또한 FPGA와 ASIC 설계 테스트를 위한 FPGA hardware-in-the-loop을 포함하는 HDL Verifier도 함께 발표하여 주목받았다. 두 제품을 통해 매스웍스는 MATLAB과 Simulink에서 동시에 HDL 코드 생성과 검증을 지원한다.

매스웍스의 임베디드 응용 프로그램 및 인증 매니저인 톰 얼키넨(Tom Erkkinen)은 “모든 엔지니어들은 시스템 및 알고리즘 설계에 MATLAB 및 Simulink를 사용한다”며, “HDL Coder 및 HDL Verifier를 사용하면 FPGA와 ASIC 설계 개발 시 수동으로 HDL 코드나 테스트 벤치를 작성해야 하는 번거로움이 없다”고 말했다.

MATLAB 함수와 Simulink 모델로부터 이식과 합성이 가능한 VHDL 및 Verilog 코드를 HDL Coder에서 생성해 FPGA 프로그래밍이나 ASIC 프로토타입화 및 설계에 사용할 수 있다. 엔지니어링 팀은 하드웨어 구현을 위한 최적의 알고리즘을 즉시 파악할 수 있다. Simulink 모델과 생성된 HDL 코드 사이에 추적이 가능해 DO-254 및 기타 표준을 준수하는 고집적 응용 프로그램의 개발을 지원할 수 있다.

HDL Verifier는 알테라(Altera) 및 자일링스 FPGA 보드를 위한 FPGA hardware-in-the-loop 검증을 지원한다. HDL Verifier는 MATLAB과 Simulink를 케이던스(Cadence) 인사이시브(Incisive), 멘토그래픽스(Mentor Graphics)의 모델심(ModelSim) 및 퀘스타(Questa)의 HDL 시뮬레이터와 연결하는 공동 시뮬레이션 인터페이스를 제공한다. 엔지니어는 HDL 구현이 MATLAB 알고리즘 및 Simulink 시스템 사양과 일치하는지 빠르게 확인할 수 있다.

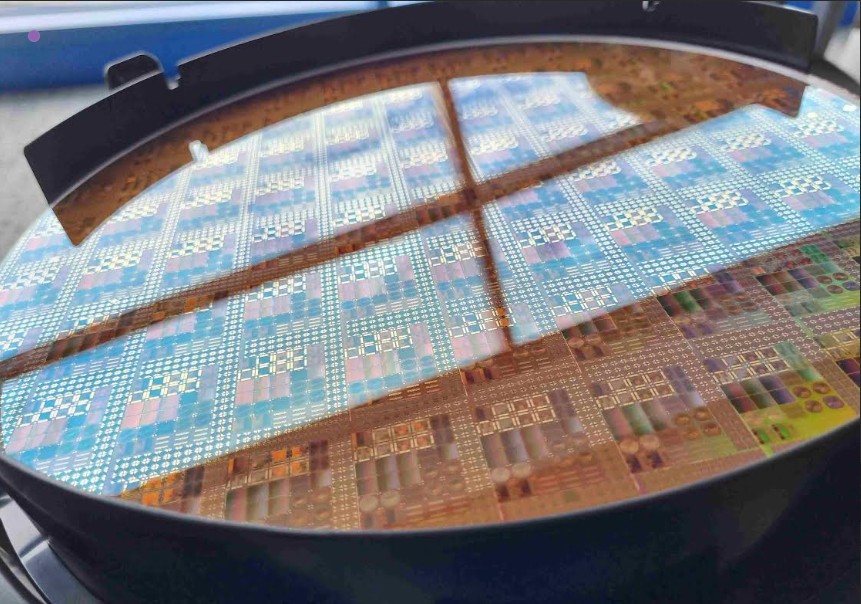

알테라 제품 및 기업 마케팅 부사장인 빈스 후(Vince Hu)는 “업계에서 FPGA의 채택이 계속 늘어감에 따라 설계자는 시스템 모델과 FPGA 설계 사이의 검증에 대한 간극을 해소할 필요가 있다”며, “HDL Verifier는 시스템 모델을 FPGA 설계로 연결하고 엔지니어가 알테라 FPGA 및 Simulink를 통해 FPGA HIL(hardware-in-the-loop) 검증을 수행할 수 있도록 지원한다. 이 워크플로는 검증 주기를 단축하고 엔지니어가 안심하고 실리콘을 구현할 수 있도록 도와 준다”고 전했다.

www.mathworks.co.kr

이벤트

MATLAB EXPO Korea 2012

매스웍스, MATLAB과 Simulink에서 동시에 HDL 코드 생성과 검증을 지원

세계적인 테크니컬 엔지니어링 소프트웨어 공급업체인 매스웍스는 6월 20일 서울 코엑스 인터컨티넨탈호텔에서 엔지니어들을 위한 매스웍스 종합기술 컨퍼런스인 MATLAB EXPO 2012를 개최했다. 이날 매스웍스는 MATLAB과 Simulink에서 동시에 HDL 코드 생성과 검증을 지원한다고 밝혔다.

MATLAB EXPO Korea 2012에서는 매스웍스 본사 프로덕트 마케팅 디렉터인 폴 버나드(Paul Barnard)가 기조 연설자로 나서 ‘Getting to Smart’를 주제로 발표했으며, 고려대학교 최진영 교수가 ‘융합소프트웨어의 새로운 기회’에 대한 초청기조연설을 진행했다.

이어서 테크니컬 컴퓨팅(Technical Computing), 설계 및 시뮬레이션(Design & Simulation), 구현 및 검증(Implementation & Verification), 매스웍스 데모 및 파트너 발표 세션 등 총 5개 트랙을 통해 MATLAB으로부터 C/HDL 자동 코드 생성, Simulink에서의 팀 단위협업, MATLAB의 Computer Vision 애플리케이션 개발 환경 및 Speeding Up 솔루션, DO-178C/ISO 26262등 산업 표준을 위한 코드 생성 및 검증, MATLAB을 이용한 계측기 제어 및 데이터 수집 분석 등 20여 개 이상의 다양하고 통찰력 있는 기술 세션을 제공했다.

또한 다양한 고객 사례 및 파트너사의 관련 솔루션 전시, 매스웍스 전문가 및 관련 업계 엔지니어들과의 네트워킹을 통해 실무 정보를 나누는 의미 있는 자리로 진행되어 참석자의 많은 호응을 받았다.

FPGA 설계와 시스템 모델 검증을 자동화

이번 매스웍스 행사에서의 최대 이슈는 MATLAB에서 자동으로 HDL 코드를 생성해 엔지니어가 FPGA와 ASIC 설계를 손쉽게 구현할 수 있도록 지원하는 새로운 버전의HDL Coder의 발표이다. 또한 FPGA와 ASIC 설계 테스트를 위한 FPGA hardware-in-the-loop을 포함하는 HDL Verifier도 함께 발표하여 주목받았다. 두 제품을 통해 매스웍스는 MATLAB과 Simulink에서 동시에 HDL 코드 생성과 검증을 지원한다.

매스웍스의 임베디드 응용 프로그램 및 인증 매니저인 톰 얼키넨(Tom Erkkinen)은 “모든 엔지니어들은 시스템 및 알고리즘 설계에 MATLAB 및 Simulink를 사용한다”며, “HDL Coder 및 HDL Verifier를 사용하면 FPGA와 ASIC 설계 개발 시 수동으로 HDL 코드나 테스트 벤치를 작성해야 하는 번거로움이 없다”고 말했다.

MATLAB 함수와 Simulink 모델로부터 이식과 합성이 가능한 VHDL 및 Verilog 코드를 HDL Coder에서 생성해 FPGA 프로그래밍이나 ASIC 프로토타입화 및 설계에 사용할 수 있다. 엔지니어링 팀은 하드웨어 구현을 위한 최적의 알고리즘을 즉시 파악할 수 있다. Simulink 모델과 생성된 HDL 코드 사이에 추적이 가능해 DO-254 및 기타 표준을 준수하는 고집적 응용 프로그램의 개발을 지원할 수 있다.

자일링스(Xilinx)의 마케팅 및 비즈니스 개발 선임 부사장인 빈 랫포드(Vin Ratford)는 “자일링스 ISE Design Suite와 통합된 HDL Coder는 알고리즘 개발자가 자일링스 FPGA를 대상으로 매스웍스 제품을 사용할 때에 사용상의 편의를 돕는 손쉬운 작업환경을 제공한다”고 말했다. 이 통합환경은 양사의 상호고객에게 생산성을 가속할 수 있도록 HDL Coder내에 Xilinx의 IP를 통합하는 기능도 제공한다.

HDL Verifier는 알테라(Altera) 및 자일링스 FPGA 보드를 위한 FPGA hardware-in-the-loop 검증을 지원한다. HDL Verifier는 MATLAB과 Simulink를 케이던스(Cadence) 인사이시브(Incisive), 멘토그래픽스(Mentor Graphics)의 모델심(ModelSim) 및 퀘스타(Questa)의 HDL 시뮬레이터와 연결하는 공동 시뮬레이션 인터페이스를 제공한다. 엔지니어는 HDL 구현이 MATLAB 알고리즘 및 Simulink 시스템 사양과 일치하는지 빠르게 확인할 수 있다.

알테라 제품 및 기업 마케팅 부사장인 빈스 후(Vince Hu)는 “업계에서 FPGA의 채택이 계속 늘어감에 따라 설계자는 시스템 모델과 FPGA 설계 사이의 검증에 대한 간극을 해소할 필요가 있다”며, “HDL Verifier는 시스템 모델을 FPGA 설계로 연결하고 엔지니어가 알테라 FPGA 및 Simulink를 통해 FPGA HIL(hardware-in-the-loop) 검증을 수행할 수 있도록 지원한다. 이 워크플로는 검증 주기를 단축하고 엔지니어가 안심하고 실리콘을 구현할 수 있도록 도와 준다”고 전했다.

아이씨엔 매거진 2012년 07월호

![[#HM26] 협동로봇의 진화, ‘보조’ 넘어 ‘산업용 핵심’으로 [#HM26] 협동로봇의 진화, ‘보조’ 넘어 ‘산업용 핵심’으로](https://icnweb.kr/wp-content/uploads/2026/05/HM26_fanuc_cobot-900web.png)

![[그래프] 국회의원 선거 결과 정당별 의석수 (19대-22대) 대한민국 국회의원 선거 결과(정당별 의석 수)](https://icnweb.kr/wp-content/uploads/2025/04/main-image-vote-flo-web-2-324x160.jpg)