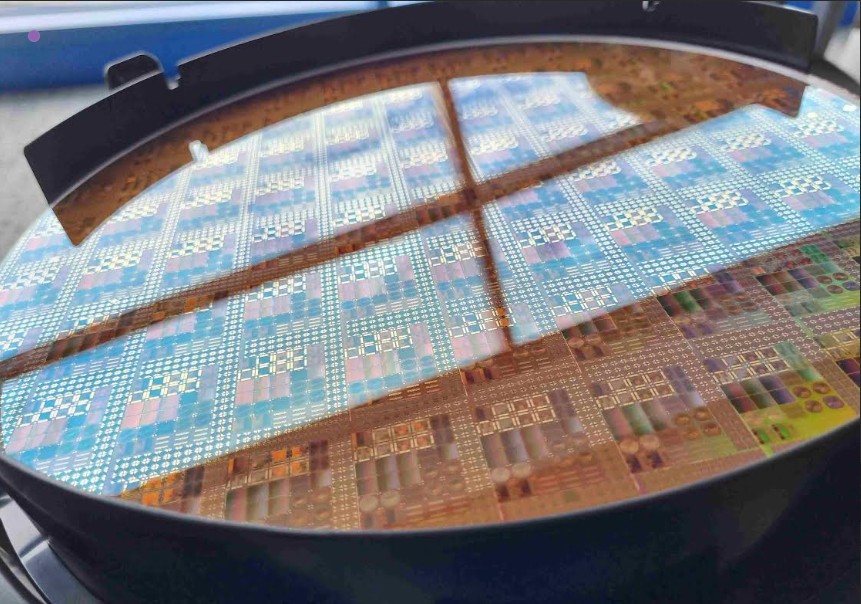

알테라와 TSMC는 알테라의 20nm Arria® 10 FPGA 및 SoC에 TSMC의 특허를 획득한 미세피치 가공 동 범프(copper bump) 기반 패키징 기술 적용을 위해 양사가 협력한다고 발표했다. 알테라는 자사의 20nm 디바이스 제품군에 품질, 신뢰성, 성능을 향상시키기 위해 업체로는 처음 상용 생산에 이 기술을 적용한다.

빌 마조티(Bill Mazotti) 알테라 국제사업부 및 엔지니어링 부사장은 “TSMC는 알테라의 Arria 10 디바이스에 최첨단의 견고한 집적 패키지 솔루션을 제공한다. Arria 10 디바이스는 업계 최고 밀도의 모노리식 20nm FPGA 다이”라고 하면서 “이 기술을 적용하는 것은 Arria 10 FPGA 및 SoC를 완벽하게 보완하고 20nm 노드의 패키징 과제를 해결하는 데 도움을 준다”고 말했다.

TSMC의 업계 선도적인 플립 칩 BGA 패키지 기술은 미세피치 가공 동 범프를 사용해 표준 동 범프 솔루션에 비해 뛰어난 품질과 신뢰성을 Arria 10 디바이스에 제공한다. 이 기술은 고성능 FPGA 제품에 요구되는 매우 많은 수의 범프를 배치할 수 있다. 또한 탁월한 범프 접합부 피로 수명과 EM(electro-migration) 전류의 향상된 성능, ELK(Extra Low-K) 레이어 상에 낮은 스트레스를 제공한다. 이러한 모든 특성은 첨단 실리콘 기술을 적용하는 제품에 매우 핵심적인 특징들이다.

데이비드 켈러(David Keller) TSMC 북미지역 사업부 총괄 부사장은 “TSMC의 동 범프 기반 패키지 기술은 ELK를 특징으로 하는 미세 범프 피치(150µm 미만)의 첨단 실리콘 제품에 탁월한 가치를 제공한다”고 하면서 “알테라가 TSMC의 고집적 패키징 기술을 채택하게 되어 기쁘다”고 말했다.

알테라는 또한 TSMC 20SoC 공정 기술을 기반으로 하고 혁신적 패키징 기술을 탑재한 Arria 10 FPGA를 출하하고 있다. Arria 10 FPGA 및 SoC는 단일 모노리식 다이에 FPGA 업계 최고 밀도를 제공하며 이전 28nm Arria 제품군 대비 최대 40% 낮은 전력을 소비한다고 강조했다.

아이씨엔 뉴스팀 news@icnweb.co.kr

![[전문가기고] K-배터리 3사, ‘Beyond EV’ 시장을 향한 기술 초격차 전략 비교 [인터배터리 2026] [전문가기고] K-배터리 3사, ‘Beyond EV’ 시장을 향한 기술 초격차 전략 비교 [인터배터리 2026]](https://icnweb.kr/wp-content/uploads/2026/03/battery-P3-beyond-Battery-web-1024x576.png)

![[심층기획] 피지컬 AI의 심장 ‘이차전지’, 휴머노이드 로봇 혁명 이끈다 [인터배터리 2026] [심층기획] 피지컬 AI의 심장 ‘이차전지’, 휴머노이드 로봇 혁명 이끈다 [인터배터리 2026]](https://icnweb.kr/wp-content/uploads/2026/03/Battery-pack-interB-Phy-AI.png)

![[칼럼] 제조업 생존 가르는 EU CRA와 피지컬 AI 보안 전략 [칼럼] 제조업 생존 가르는 EU CRA와 피지컬 AI 보안 전략](https://icnweb.kr/wp-content/uploads/2026/03/CRA-2026-notebookLM-20260326-1024web.png)

![[그래프] 국회의원 선거 결과 정당별 의석수 (19대-22대) 대한민국 국회의원 선거 결과(정당별 의석 수)](https://icnweb.kr/wp-content/uploads/2025/04/main-image-vote-flo-web-2-324x160.jpg)

![[#HM24] HARTING, 미래 핵심인 전기에너지에 열정을 쏟다 [#HM24] HARTING, 미래 핵심인 전기에너지에 열정을 쏟다](https://icnweb.kr/wp-content/uploads/2024/04/HM24-HARTING_TECO-2030-900web.jpg)

![[#HM24] 안전한 데이터 교환의 상생적 이점 [#HM24] 안전한 데이터 교환의 상생적 이점](https://icnweb.kr/wp-content/uploads/2024/04/roseman-labs-hm24_3_2-1024x683.jpg)

![[#HM24] 벡호프, AI 모델 생성을 간소화하는 AutoML 도구 출시 [#HM24] 벡호프, AI 모델 생성을 간소화하는 AutoML 도구 출시](https://icnweb.kr/wp-content/uploads/2024/04/TwinCAT-ML-Creator-Dr-Fabian-web.png)