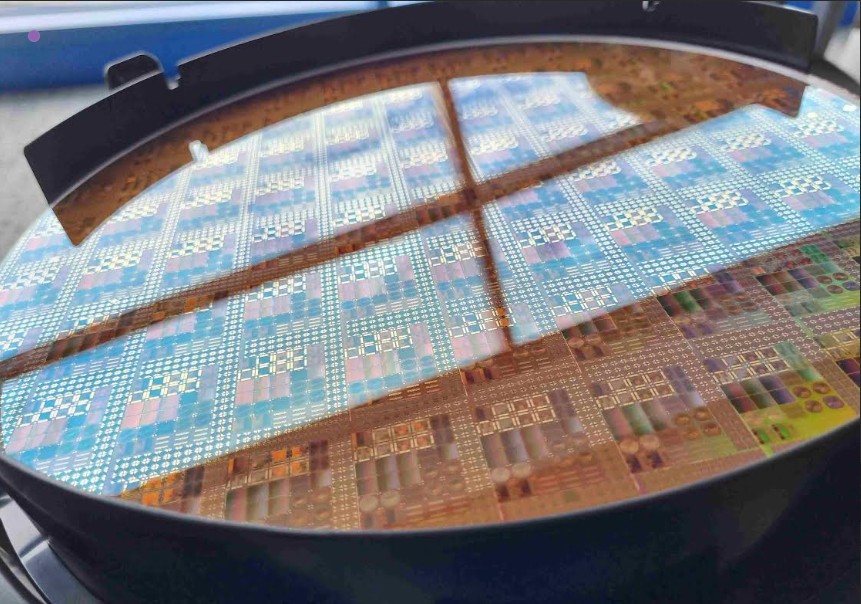

자일링스는 프로그래머블 업계 최초의 SoC 강도 디자인 수트인 비바도™ 디자인 수트(Vivado™ Design Suite)를 새롭게 선보이며, 두 가지 주요한 생산성 개선 사항을 발표했다.

비바도 디자인 수트 2013.1 릴리즈는 보다 빠른 시스템 통합을 위해 새로운 IP 중심의 디자인 환경과 빠른 C/C++ 시스템 레벨 디자인 및 HLS(High-Level Synthesis)를 지원하는 종합 라이브러리 세트를 포함하고 있다.

IP 창출 및 통합 가속화

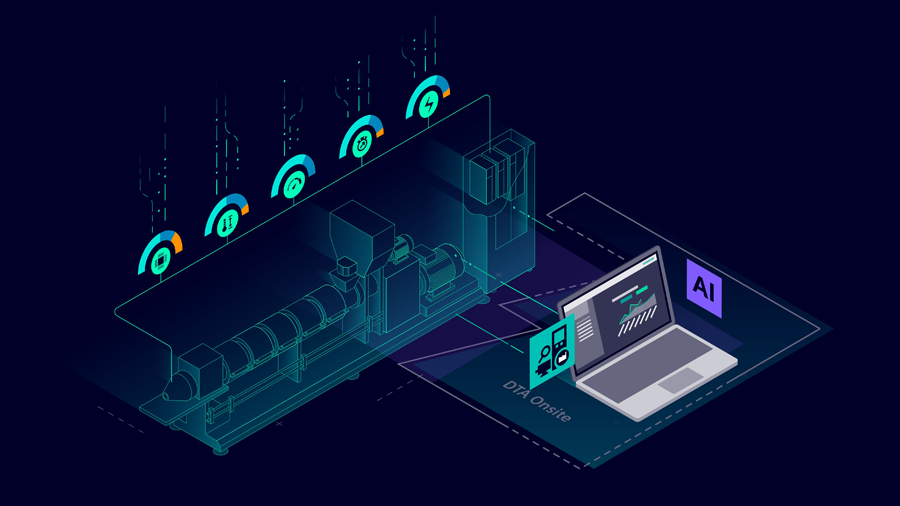

자일링스는 올 프로그래머블 FPGA 디바이스에서 고집적, 복잡한 디자인 작업 속도를 높이기 위해, 비바도 IPI(IP Integrator)의 얼리 액세스(early access) 릴리즈를 출시했다. 비바도 IPI를 사용하면 RTL, 자일링스 IP, 서드파티IP, C/C++ 합성 IP 등을 빠르게 통합할 수 있다.

또한 IPI는 ARM AXI 인터커넥트 및 IP 패키징용 IP XACT와 같은 산업 표준에 기반하고 있으며, 자일링스 올 프로그래머블 솔루션에 최적화된 지능형 오류 제거 기술(correct-by-construction) 어셈블리 기능을 제공한다.

IPI는 비바도 디자인 수트를 기반으로 IP인식 자동 AXI 인터커넥트, 원 클릭(one-click) IP 서브시스템 세대, 실시간 DRC, 인터페이스 변경 전달, 강력한 디버그 기능을 갖춘 디바이스이자 그래픽 스크립터블 쌍방향 플랫폼 인식(platform aware interactive, graphical and scriptable) 환경이라고 할 수 있다.

특히 Zynq™-7000 올 프로그래머블 SoC를 대상으로 하는 임베디드 디자이너들이 IPI를 사용하면 듀얼 코어 ARM 프로세싱 시스템 및 고성능 FPGA 패브릭을 목표로 하는 소프트웨어 및 하드웨어 IP를 보다 빠르게 확인하고 재사용, 통합할 수 있다.

아토믹 룰스 LLC(Atomic Rules LLC)의 CTO인 셰퍼드 시겔(Shep Siegel)은 “비바도는 자사의 RCC(reconfigurable computing) 플랫폼과 애플리케이션 개발 생산성을 크게 향상시켰다.”며, “비바도 IPI 와 7 시리즈 실리콘의 결합으로 개발 일정을 앞당길 수 있었다. 고객의 요구를 해결하기 위해 실리콘과 디자인 흐름에서 자일링스가 보여준 혁신은 매우 인상적이다.”라고 덧붙였다.

빠른 시스템 레벨 디자인을 위한 라이브러리

C/C++ 시스템 레벨 디자인과 HLS를 가속화하기 위해, 자일링스는 산업 표준 부동소수점 math.h 연산과 실시간 비디오 프로세싱 기능을 지원하여 비바도 HLS 라이브러리를 강화했다.

비바도 HLS를 평가한 350 명 이상의 사용자와 1,000 개 이상의 고객사는 이제 듀얼코어 ARM 프로세싱 시스템에서 실행되는 임베디드 비전을 위해 OpenCV 환경에 통합된 비디오 프로세싱 기능에 바로 접근할 수 있다.

또한 최신 솔루션은 하드웨어 가속을 통해 기존 C/C++ 알고리즘의 성능을 최대 100배까지 개선시킴과 동시에 비바도 HLS는 RTL 디자인 엔트리 플로우(entry flow)보다 시스템 검증 및 구현 시간을 최대 100배까지 앞당겨 준다.

또한 고성능 FPGA 패브릭에서 자동 가속되는 연산 강화 기능(compute intensive function)을 통해 Zynq-7000 올 프로그래머블 SoC를 사용하는 디자이너들은 보다 빠르게 듀얼 코어 ARM 프로세싱 시스템을 위한 C/C++ 코드를 개발할 수 있다. ©

www.altera.com

아이씨엔 매거진 2013년 05월호

![[전문가기고] K-배터리 3사, ‘Beyond EV’ 시장을 향한 기술 초격차 전략 비교 [인터배터리 2026] [전문가기고] K-배터리 3사, ‘Beyond EV’ 시장을 향한 기술 초격차 전략 비교 [인터배터리 2026]](https://icnweb.kr/wp-content/uploads/2026/03/battery-P3-beyond-Battery-web-1024x576.png)

![[심층기획] 피지컬 AI의 심장 ‘이차전지’, 휴머노이드 로봇 혁명 이끈다 [인터배터리 2026] [심층기획] 피지컬 AI의 심장 ‘이차전지’, 휴머노이드 로봇 혁명 이끈다 [인터배터리 2026]](https://icnweb.kr/wp-content/uploads/2026/03/Battery-pack-interB-Phy-AI.png)

![[칼럼] 제조업 생존 가르는 EU CRA와 피지컬 AI 보안 전략 [칼럼] 제조업 생존 가르는 EU CRA와 피지컬 AI 보안 전략](https://icnweb.kr/wp-content/uploads/2026/03/CRA-2026-notebookLM-20260326-1024web.png)

![[그래프] 국회의원 선거 결과 정당별 의석수 (19대-22대) 대한민국 국회의원 선거 결과(정당별 의석 수)](https://icnweb.kr/wp-content/uploads/2025/04/main-image-vote-flo-web-2-324x160.jpg)

![[#HM24] HARTING, 미래 핵심인 전기에너지에 열정을 쏟다 [#HM24] HARTING, 미래 핵심인 전기에너지에 열정을 쏟다](https://icnweb.kr/wp-content/uploads/2024/04/HM24-HARTING_TECO-2030-900web.jpg)

![[#HM24] 안전한 데이터 교환의 상생적 이점 [#HM24] 안전한 데이터 교환의 상생적 이점](https://icnweb.kr/wp-content/uploads/2024/04/roseman-labs-hm24_3_2-1024x683.jpg)