유선 및 데이터 센터 상호 연결을 위해 차세대 이더넷 배치를 가속화하는 디바이스

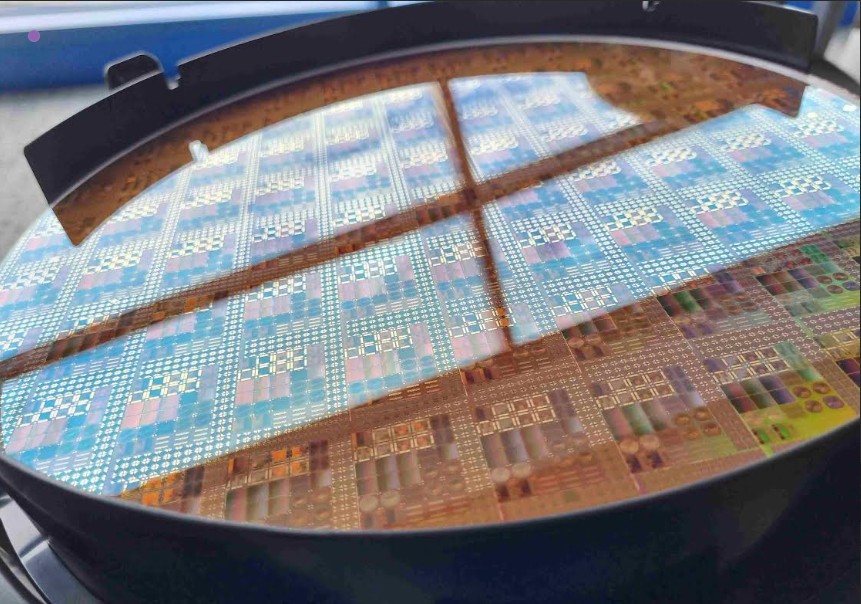

자일링스는 업계를 선도하고 있는 버텍스 울트라스케일+(Virtex® UltraScale+™) FPGA에 56G PAM4 트랜시버 기술을 통합한다고 발표했다. 16나노 핀펫(FinFET)+ FPGA 패브릭에 구축되고 검증된 이 디바이스는 버텍스 제품 라인을 확장시켜 차세대 이더넷 배치를 제공하고, 기존 시스템을 차세대 백플레인, 광학 및 고성능 인터커넥트에 유연하게 마이그레이션 한다.

유선 통신, 데이터 센터 및 무선 백홀 애플리케이션을 대상으로 하는 통합 디바이스를 사용하면, 고객은 56G+ 라인 속도에서 데이터 전송의 물리적인 한계를 극복함으로써 기존의 인프라에서 대역폭을 두 배로 늘릴 수 있다.

자일링스의 SerDes 테크놀로지 그룹 부사장인 켄 창(Ken Chang)은 ”자일링스는 16나노 FPGA에 56G PAM4를 결합해 트랜시버 기술을 주도하고 있다”며, ”이러한 새로운 디바이스는 검증된 FPGA를 기반으로 구축되며, 곧 배치될 광학, ASIC 및 백플레인과 함께 다양하게 활용될 것이다”라고 전했다.

이번 발표를 통해 자일링스는 2016년에 16나노 프로그래머블 디바이스에서 56G PAM4 트랜시버 기술을 최초로 선보인 이후, 또 다른 기술적인 혁신을 주도하고 있음을 보여줬다.

오승모 기자 oseam@icnweb.co.kr

![[전문가기고] K-배터리 3사, ‘Beyond EV’ 시장을 향한 기술 초격차 전략 비교 [인터배터리 2026] [전문가기고] K-배터리 3사, ‘Beyond EV’ 시장을 향한 기술 초격차 전략 비교 [인터배터리 2026]](https://icnweb.kr/wp-content/uploads/2026/03/battery-P3-beyond-Battery-web-1024x576.png)

![[심층기획] 피지컬 AI의 심장 ‘이차전지’, 휴머노이드 로봇 혁명 이끈다 [인터배터리 2026] [심층기획] 피지컬 AI의 심장 ‘이차전지’, 휴머노이드 로봇 혁명 이끈다 [인터배터리 2026]](https://icnweb.kr/wp-content/uploads/2026/03/Battery-pack-interB-Phy-AI.png)

![[칼럼] 제조업 생존 가르는 EU CRA와 피지컬 AI 보안 전략 [칼럼] 제조업 생존 가르는 EU CRA와 피지컬 AI 보안 전략](https://icnweb.kr/wp-content/uploads/2026/03/CRA-2026-notebookLM-20260326-1024web.png)

![[그래프] 국회의원 선거 결과 정당별 의석수 (19대-22대) 대한민국 국회의원 선거 결과(정당별 의석 수)](https://icnweb.kr/wp-content/uploads/2025/04/main-image-vote-flo-web-2-324x160.jpg)

![[#HM24] 안전한 데이터 교환의 상생적 이점 [#HM24] 안전한 데이터 교환의 상생적 이점](https://icnweb.kr/wp-content/uploads/2024/04/roseman-labs-hm24_3_2-1024x683.jpg)

![[#HM24] HARTING, 미래 핵심인 전기에너지에 열정을 쏟다 [#HM24] HARTING, 미래 핵심인 전기에너지에 열정을 쏟다](https://icnweb.kr/wp-content/uploads/2024/04/HM24-HARTING_TECO-2030-900web.jpg)

![[#HM24] 벡호프, AI 모델 생성을 간소화하는 AutoML 도구 출시 [#HM24] 벡호프, AI 모델 생성을 간소화하는 AutoML 도구 출시](https://icnweb.kr/wp-content/uploads/2024/04/TwinCAT-ML-Creator-Dr-Fabian-web.png)