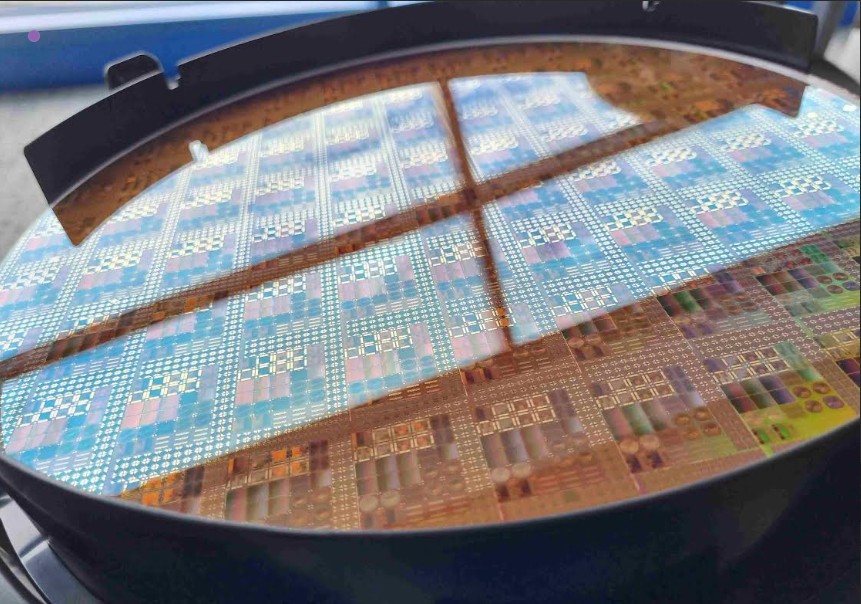

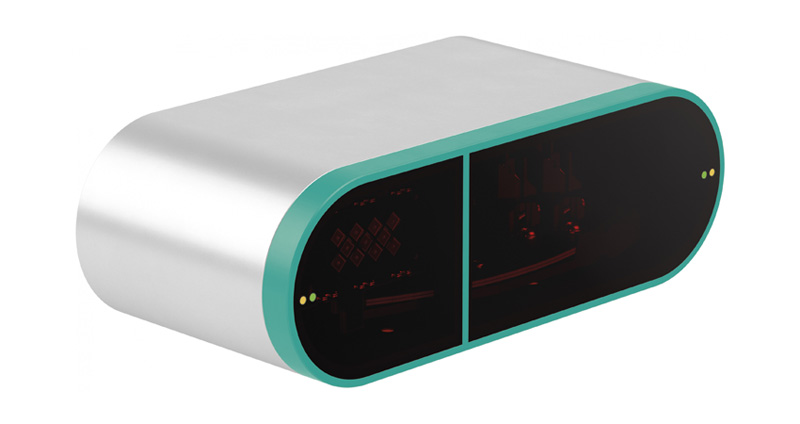

텍사스인스트루먼트(이하, TI; www.ti.com)는 모바일 월드 콩그레스(MWC) 2014에서 0.3인치의 HD TRP(Tilt & Roll Pixel) DLP® Pico™ 칩셋을 선보였다.

이번에 공개된 칩셋은 최소형, 최대 전력 효율의 HD 해상도의 마이크로 미러 어레이를 갖추고 있어 태블릿, 스마트폰, 액세서리, 웨어러블 디스플레이, 증강현실 디스플레이, 인터액티브 서피스 컴퓨팅(interactive surface computing), 디지털 사이니지 및 컨트롤 패널을 포함한 소형 전자기기에서 고화질(HD) 디스플레이를 구현할 수 있다. 이미 입증된 DLP Cinema® 기술에 기반한 새로운 DLP Pico 칩은 밝고 선명한 고품질의 HD 영상을 제공한다.

새로운 0.3” HD TRP 칩셋은 TI 고유의 TRP(Tilt & Roll Pixel) DLP 아키텍처와 적응형 인텔리브라이트(IntelliBrightTM) 알고리즘 스위트를 사용하여 기존 DLP Pico 아키텍처보다 밝기를 높이고 소비 전력을 줄였다. 또한, 스위칭 속도가 최대 초당 수천 회에 달하여, 120Hz 비디오 성능을 갖춘 가장 작은 트루컬러 RGB 엔진을 구현한다.

완제품 개발이 더 빨리 진행될 수 있도록, TI는 업계에서 가장 광범위한 Pico 에코시스템을 유지하면서 적극적으로 선두 개발업체 및 제조 업체들과 0.3” HD TRP 칩셋을 이용한 제품을 2014년에 출시할 수 있도록 협력하고 있다. 아시아 옵티컬(Asia Optical), 세코닉스(Sekonix), 심천 안화 옵토일렉트로닉스 테크놀로지(Shenzhen Anhua Optoelectronics Technology. Co. LTD), 유니드일렉트로(UneedElectro Inc.), 영옵틱스(Yong Optics) 등의 업계 유수의 광학 엔진 제조업체들이 참여하는 DLP 에코 시스템 회원사에 문의하면 보다 자세한 정보를 확인할 수 있다.

TI DLP Pico 사업부 매니저 프랭크 모이지오(Frank Moizio)는 “이 HD 칩셋은 DLP에 있어서 중요한 이정표라고 할 수 있다. TI는 프레임-바이-프레임(frame-by-frame) 기준으로 기존 아키텍처 대비 0.3인치의 MEMS 디바이스에서 2배의 픽셀을 구현하고, 30% 높은 광학 효율과 최대 50%까지 전력 절감이 가능하다.”고 말했다.

아이씨엔 오승모 기자 oseam@icnweb.co.kr

![[전문가기고] K-배터리 3사, ‘Beyond EV’ 시장을 향한 기술 초격차 전략 비교 [인터배터리 2026] [전문가기고] K-배터리 3사, ‘Beyond EV’ 시장을 향한 기술 초격차 전략 비교 [인터배터리 2026]](https://icnweb.kr/wp-content/uploads/2026/03/battery-P3-beyond-Battery-web-1024x576.png)

![[심층기획] 피지컬 AI의 심장 ‘이차전지’, 휴머노이드 로봇 혁명 이끈다 [인터배터리 2026] [심층기획] 피지컬 AI의 심장 ‘이차전지’, 휴머노이드 로봇 혁명 이끈다 [인터배터리 2026]](https://icnweb.kr/wp-content/uploads/2026/03/Battery-pack-interB-Phy-AI.png)

![[칼럼] 제조업 생존 가르는 EU CRA와 피지컬 AI 보안 전략 [칼럼] 제조업 생존 가르는 EU CRA와 피지컬 AI 보안 전략](https://icnweb.kr/wp-content/uploads/2026/03/CRA-2026-notebookLM-20260326-1024web.png)

![[그래프] 국회의원 선거 결과 정당별 의석수 (19대-22대) 대한민국 국회의원 선거 결과(정당별 의석 수)](https://icnweb.kr/wp-content/uploads/2025/04/main-image-vote-flo-web-2-324x160.jpg)

![[#HM24] 안전한 데이터 교환의 상생적 이점 [#HM24] 안전한 데이터 교환의 상생적 이점](https://icnweb.kr/wp-content/uploads/2024/04/roseman-labs-hm24_3_2-1024x683.jpg)

![[#HM24] HARTING, 미래 핵심인 전기에너지에 열정을 쏟다 [#HM24] HARTING, 미래 핵심인 전기에너지에 열정을 쏟다](https://icnweb.kr/wp-content/uploads/2024/04/HM24-HARTING_TECO-2030-900web.jpg)

![[#HM24] 벡호프, AI 모델 생성을 간소화하는 AutoML 도구 출시 [#HM24] 벡호프, AI 모델 생성을 간소화하는 AutoML 도구 출시](https://icnweb.kr/wp-content/uploads/2024/04/TwinCAT-ML-Creator-Dr-Fabian-web.png)