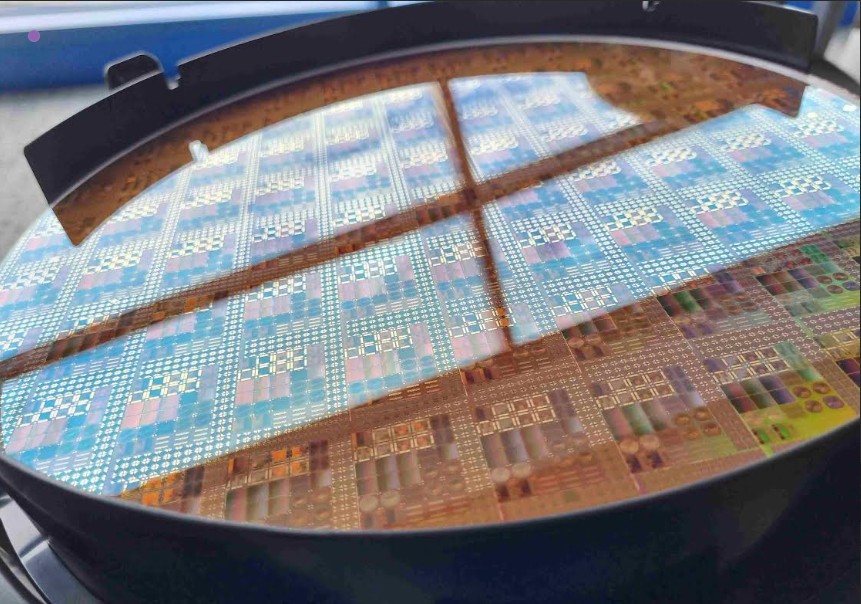

반도체 제품의 기능성과 속도, 저전력 소비를 높이려면 포토 리소그래피를 활용한 반도체 소형화 기술이 필요하다. 하지만 공정의 복잡성과 높은 비용으로 인해 소형화는 한계에 다다르고 있다. 이러한 문제를 극복하기 위해 차세대 반도체 패키징 기술이 주목받고 있다. 인터포저 표면에 여러 칩(CPI, AI 프로세서, 메모리 등)을 고밀도로 장착해 처리 속도를 향상하는 기술이다.

이에 따라 다이니폰프린팅(Dai Nippon Printing)이 여러 반도체 칩과 기판을 전기적으로 연결하는 고성능 중간 부품 ‘인터포저(interposer)’를 개발했다. 이 인터포저는 차세대 반도체 패키지에서 중요한 역할을 할 것으로 기대된다.

이와 함께 DNP는 2024년 양산을 목표로 부품 기능을 추가로 개발하기 위해 JOINT2(Jisso Open Innovation of Tops 2)에 참여했다. JOINT2는 반도체 패키지 재료, 기판, 장비를 개발하는 12개 기업으로 이뤄진 컨소시엄이다. 주관사는 쇼와 덴코 머티리얼(Showa Denko Materials Co., Ltd.)로 신에너지 산업기술개발기구(NEDO)의 ‘5G 이후 정보 통신 시스템을 위한 인프라 개선’ 연구 개발 프로젝트에 선정됐다.

이 인터포저는 배선 저항성 증가 및 배선층 절연 저항 열화 문제를 극복해 첨단 반도체 패키징에 필요한 고성능을 구현한다.

DNP는 인쇄 공정에 기반한 미세가공(microfabrication) 기술을 적용해 차세대 패턴 전송 기술인 나노임프린트 리소그래피용 템플릿을 제조한다. 또한 센서를 위한 MEMS(마이크로 전자 시스템) 파운드리 서비스를 통해 사업을 확장하고 있다. 이번 최신 개발은 고급 패키징 기술을 위해 앞서 언급한 사업을 통해 개발된 유리 및 실리콘 기판 공정과 함께 처리 기술, 미세 배선 형성 기술을 적용했다.

DNP 연구/사업개발센터의 오히가시 료이치(Ryoichi Ohigashi)는 “DNP는 JOINT2에 참여한 다른 기업들과 협력해 인터포저의 기능을 추가로 개발하고 2024년 양산을 위한 이니셔티브를 발전시켜 나갈 것”이라며 “차세대 반도체 패키지 기술 개발에도 힘을 쏟을 계획”이라고 밝혔다.

![[#HM26] 협동로봇의 진화, ‘보조’ 넘어 ‘산업용 핵심’으로 [#HM26] 협동로봇의 진화, ‘보조’ 넘어 ‘산업용 핵심’으로](https://icnweb.kr/wp-content/uploads/2026/05/HM26_fanuc_cobot-900web.png)

![[그래프] 국회의원 선거 결과 정당별 의석수 (19대-22대) 대한민국 국회의원 선거 결과(정당별 의석 수)](https://icnweb.kr/wp-content/uploads/2025/04/main-image-vote-flo-web-2-324x160.jpg)